The AeroQor<sup>®</sup> Isolated PFC Module is a high efficiency, active PFC, AC-DC converter designed to be used as a COTS Component in airborne applications. It operates from a universal AC input and generates an isolated DC output. Regulated output and droop output modules are available. Used in conjunction with a hold-up capacitor, and SynQor's AC line filter, the AeroQor will draw a nearly perfect sinusoidal current (PF>0.99) from a single phase AC input. The module is designed with a high level of documentation and traceability.

#### **Operational Features**

- · Isolated output, 600W output power

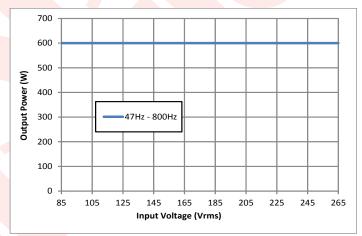

- Universal input frequency range: 47 63Hz / 360 800Hz

- Input voltage range: 85-264Vrms

- Output remains in regulation during input dropout event

- High efficiency: 90% (115Vrms), ≥0.99 Power Factor

- · Minimal inrush current

- Secondary side control pins with 3.3V standby power

- Can be paralleled (droop version only)

#### **Control Features**

- PFC Enable input

- AC and DC Power Good Signal

- 3.3V secondary standby power; UART interface

#### **Protection Features**

- · Input current limit and auto-recovery short circuit protection

- Auto-recovery input under/over-voltage protection

- Auto-recovery output over-voltage protection

- Auto-recovery thermal shutdown

#### **Mechanical Features**

- Industry standard full-brick package

- Size: 2.486" x 4.686" x 0.512" (63.14 x 119.02 x 13.0 mm)

- Total weight: 11.3oz (320g)

- Flanged baseplate version available

VUTF

VUTF

VUTF

Designed and manufactured in the USA

#### **Specification Compliance**

- RTCA/DO-160

- Airbus ABD0100.1.8

- Boeing 787B3-0147

- Boeing D6-36440

- Boeing D6-44588

#### **Safety Features**

- Input to Output reinforced isolation 4250Vdc

- Input/Output to baseplate isolation 2500Vdc

- CE Marked Pending

#### **Contents**

|                            | Page No. |

|----------------------------|----------|

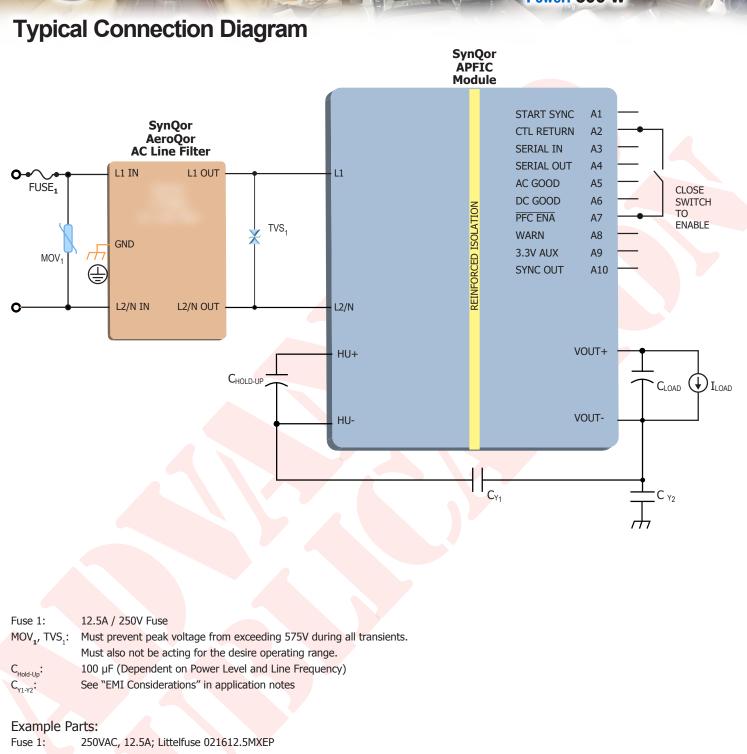

| Typical Connection Diagram | 2        |

| Technical Specification    |          |

| Standards & Qualification  | 9        |

| Application Section        | 10       |

| Encased Mechanical         | 16       |

| Ordering Information       | 18       |

Page 1

APFIC-U-55xH-FG-x Input: 85-264 Vrms Output: 55 Vdc

**Power: 600 W**

| Fuse 1:                | 250VAC, 12.5A; Littelfuse 021612.5MXEP                                                                    |

|------------------------|-----------------------------------------------------------------------------------------------------------|

| MOV <sub>1</sub> :     | 300VAC, 60J; EPCOS S10K300E2                                                                              |

| TVS <sub>1</sub> :     | 400V, 3J; two VISHAY 1.5KE200CA devices connected in series                                               |

| C <sub>Hold-Up</sub> : | One 450V, 330uF; EPCOS B43508B5337M                                                                       |

| C <sub>Y1</sub> :      | 10nF equivalence (Two paralleled banks of 2x 10nF capacitors in series), Knowles Syfer 2220YA250103KXTB16 |

| C <sub>y2</sub> :      | 10nF, 250VAC; Knowles Syfer 2220YA250103KXTB16                                                            |

| C <sub>Y2</sub> .      |                                                                                                           |

Figure A: Typical Application of the APFIC module to create a multiple-output AC-DC Power Supply

ynQoi

# **Technical Specification**

#### **APFIC-U-55xH-FG-x Electrical Characteristics**

Operating conditions of 115Vrms, 400Hz input, 10.9A output,  $600\mu$ F bulk capacitance, 1mF output capacitance, baseplate at 25°C; full operating baseplate temperature range is -40 °C to +100 °C with appropriate power derating. Specifications subject to change without notice.

| Parameter                                                | Min. | Тур.     | Max.  | Units   | Notes & Conditions                                                     |

|----------------------------------------------------------|------|----------|-------|---------|------------------------------------------------------------------------|

| ABSOLUTE MAXIMUM RATINGS<br>Input Voltage (L1 to L2/N)   | 1    | 1        | 575   | Viela   |                                                                        |

|                                                          |      |          |       | Vpk     | Car Nata 4                                                             |

| Isolation Voltage (Input to Output)                      |      |          | 4250  | Vdc     | See Note 4                                                             |

| Isolation Voltage (Input/Output to Baseplate)            | 10   |          | 2500  | Vdc     | See Note 4                                                             |

| Operating Temperature                                    | -40  |          | 100   | °C      | Baseplate temperature                                                  |

| Storage Temperature                                      | -55  |          | 125   | °C      |                                                                        |

| SERIAL IN and PFC ENA inputs                             | -2   |          | 7     | V       | Relative to CTL RETURN pin                                             |

| AC GOOD, DC GOOD, and WARN outputs                       |      |          |       |         |                                                                        |

| Pull Up Voltage                                          | -2   |          | 7     | V       | Relative to CTL RETURN pin                                             |

| Sink Current                                             |      |          | 10    | mA      |                                                                        |

| INPUT CHARACTERISTICS                                    |      |          |       |         |                                                                        |

| Operating Input Voltage Range                            |      |          |       |         |                                                                        |

| AC Input Continuous                                      | 85   |          | 264   | Vrms    |                                                                        |

| AC Input 100ms Transient                                 | 40   |          | 290   | Vrms    |                                                                        |

| input Under-Voltage Lockout                              |      | 30       |       | Vrms    | >1s duration                                                           |

| nput Over-Voltage Shutdown                               |      | 440      |       | Vpk     |                                                                        |

| Dperating Input Frequency                                | 47   | 110      | 800   | Hz      |                                                                        |

| Power Factor of AC Input Current                         | 17   |          | 000   | 112     |                                                                        |

| 50/60Hz                                                  |      | 0.99     |       |         | min 400W output (with SynQor ACF filter)                               |

|                                                          |      |          |       |         | min 400W output (with SynQor ACF filter)                               |

| 400Hz                                                    |      | 0.97     | 24    | MAD     | min 400W output (with SynQor ACF filter)                               |

| Reactive Power                                           |      | 4.5      | 34    | VAR     | 115 Vrms 400Hz; leading, see Note 5                                    |

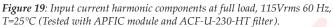

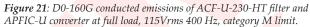

| Total Harmonic Distortion of AC Input Current            |      | 4.5      |       | %       | 115 Vrms 400Hz, full load, see Note 1                                  |

| ndividual Current Harmonic Distortion Levels at 115 Vrms |      |          |       |         | Below DO-160G/787B3/ABD0100.1.8                                        |

| nrush of AC Input Current                                |      |          | 1     | Apk     | Meets DO-160G section 16.7.5, see Note 7                               |

| inabled AC Input Current (no load)                       |      | 180      |       | mArms   | 115 Vrms input, when used with SynQor filter                           |

| Disabled AC Input Current                                |      | 50       |       | mArms   | 115 Vrms input, when used with SynQor filter                           |

| Iaximum Input Power                                      |      |          | 750   | W       |                                                                        |

| Aaximum Input Current                                    |      |          | 9.0   | Arms    | 85 Vrms input                                                          |

| OUTPUT CHARACTERISTICS                                   |      |          |       |         |                                                                        |

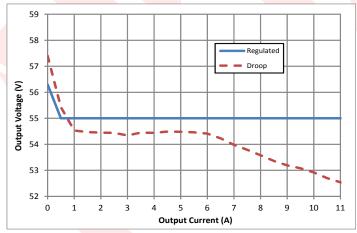

| Output Voltage Set Point at Full Load                    |      |          |       |         | See Figure 11 for V-I curve                                            |

| Standard Option                                          | 54.4 | 55.0     | 55.6  | Vdc     | Vin<250Vrms, for higher Vin see application notes                      |

| Droop Option                                             | 52.0 | 52.6     | 53.2  | Vdc     | vin 250 vinis, for higher vin see application notes                    |

| Droop Option, Current Share Analysis                     | 52.4 | 52.6     | 52.8  | Vdc     | Tolerance for droop share operation, see Note 6                        |

| Ental Output Voltage Bange                               | 52.4 | 52.0     | 52.0  | vuc     |                                                                        |

| Total Output Voltage Range                               | 540  |          | 57.0  | ) / d a | See Figure 11 for V-I curve                                            |

| Standard Option                                          | 54.0 |          | 57.0  | Vdc     | Vin<250Vrms, for higher Vin see application notes                      |

| Droop Option                                             | 52.0 |          | 58.0  | Vdc     |                                                                        |

| Standard Option Voltage Regulation                       |      |          |       |         | Above half load                                                        |

| Over Line                                                |      | ±0.3     |       | %       | Vin<250Vrms, for higher Vin see application notes                      |

| Over Load                                                |      | ±2.0     |       | %       |                                                                        |

| Over Temperature                                         |      | ±1.5     |       | %       |                                                                        |

| Dutput Voltage Ripple and Noise at 400Hz                 |      |          |       |         | Full load, see Note 2                                                  |

| Peak-to-Peak                                             |      |          | 1.0   | %       |                                                                        |

| RMS                                                      |      |          | 0.3   | %       |                                                                        |

| Derating Output Current Range                            | 0    |          | 10.9  | A       |                                                                        |

| Dutput Current Limit                                     |      |          | 10.5  | Л       | Unit continues to operate for 1s before shutdown                       |

| 115 Vrms                                                 |      | 12       |       | А       | For standard option                                                    |

| 110 11110                                                |      | 12       |       |         |                                                                        |

| 230 Vrms                                                 | -    | 13       | 2 000 | A       | For standard option                                                    |

| Aaximum Output Capacitance                               |      | 500      | 2,000 | μF      | At half resistive load                                                 |

| 1inimum Output Capacitance                               |      | 500      |       | μF      |                                                                        |

| HOLD-UP CHARACTERISTICS                                  |      |          |       |         |                                                                        |

| ypical Hold-up Voltage                                   |      | 400      |       | Vdc     |                                                                        |

| fold-up Voltage Range                                    | 380  |          | 435   | Vdc     | Hold-up voltage varies with load                                       |

| Hold-up Over-Voltage Protection Threshold                | 440  |          | 460   | Vdc     |                                                                        |

| Hold-up Under-Voltage Shutdown Threshold                 |      | 200      |       | Vdc     |                                                                        |

|                                                          | 100  |          | 1000  | μF      | See Note 3                                                             |

|                                                          |      |          |       |         |                                                                        |

| Hold-up Capacitance                                      | 100  |          |       |         |                                                                        |

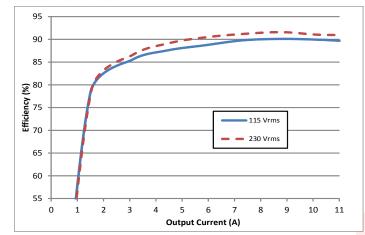

| Hold-up Capacitance                                      | 100  | 90       |       |         | See Figure 1 for efficiency curve                                      |

| Hold-up Capacitance                                      |      | 90<br>92 |       | %       | See Figure 1 for efficiency curve<br>See Figure 1 for efficiency curve |

Note 1: Individual current harmonic distortion Levels below D0-160, Airbus0100.1.8, Boeing 787B3 Requirements

Rev. 2

Note 2: 600μF electrolytic hold-up capacitor having a typical ESR of 0.5Ω. Ripple amplitude dependent on capacitance and ESR of hold-up capacitor.

Note 3: The converter is able to operate with a minimum of 100μF of hold-up capacitance, but SynQor recommends at least 330μF if the power system will be required to conform to lightning surge standards. The converter relies on the hold-up capacitor to absorb the energy from a lightning surge.

Note 4: 1 minute for qualification test, and less than 1 minute in production.

# **Technical Specification**

#### **APFIC-U-55xH-FG-x Electrical Characteristics**

Operating conditions of 115Vrms, 400Hz input, 10.9A output, 600µF bulk capacitance, 1mF output capacitance, baseplate at 25°C; full operating baseplate temperature range is -40 °C to +100 °C with appropriate power derating. Specifications subject to change without notice.

| Parameter                                                                    | Min.   | Тур.      | Max.       | Units        | Notes & Conditions                                                                       |

|------------------------------------------------------------------------------|--------|-----------|------------|--------------|------------------------------------------------------------------------------------------|

| ISOLATION CHARACTERISTICS (Input to output)                                  | 1      |           |            |              | Cas Abashita Maximum Datis as Nata 4                                                     |

| Isolation Test Voltage (Dielectric Strength)                                 | 100    |           |            | мо           | See Absolute Maximum Ratings, Note 4                                                     |

| Isolation Resistance                                                         | 100    | 100       |            | MΩ           |                                                                                          |

| Isolation Capacitance                                                        |        | 100       |            | рF           |                                                                                          |

| ISOLATION CHARACTERISTICS (Input/output to base                              | plate) |           |            |              | Cae Abaelute Maximum Patinga Nate 4                                                      |

| Isolation Test Voltage (Dielectric Strength)                                 | 100    |           |            | мо           | See Absolute Maximum Ratings, Note 4                                                     |

|                                                                              | 100    |           |            | MΩ           |                                                                                          |

| TEMPERATURE LIMITS FOR POWER DERATING CURVE                                  | 5      |           | 105        | 00           |                                                                                          |

| Semiconductor Junction Temperature                                           |        |           | 125<br>125 | °C<br>°C     |                                                                                          |

| Board Temperature<br>Fransformer Temperature                                 |        |           |            | °C           |                                                                                          |

| Maximum Baseplate Temperature, T                                             |        |           | 125<br>100 | °C           |                                                                                          |

| Dver-Temperature Protection                                                  |        |           | 100        | -0           | Measured at surface of internal PCB                                                      |

| Disable Threshold                                                            |        | 125       |            | °C           | Measured at surface of internal PCD                                                      |

| Warning Threshold                                                            |        | 120       |            | °C           | Warning causes WARN pin to go high                                                       |

| Enable Threshold                                                             |        | 120       |            | °C           | Warning causes warn pin to go nigh                                                       |

| FEATURE CHARACTERISTICS                                                      |        | 120       |            | C            |                                                                                          |

| Hold-up Capacitor Precharge                                                  |        |           |            |              |                                                                                          |

| Precharge Current                                                            |        | 50        |            | mA           |                                                                                          |

| Hold-up Short-Circuit Withstand                                              |        | 50        | indefinite | S            |                                                                                          |

| Free Running Switching Frequency                                             |        | 200       | indefinite | kHz          |                                                                                          |

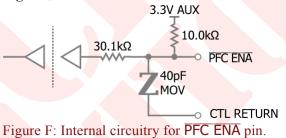

| PFC ENA (negative logic)                                                     |        | 200       |            | IXI IZ       | PFC enable input (pull low to enable unit)                                               |

| Off State Input Voltage                                                      | 2.4    |           |            | V            | The chable input (pair low to chable anit)                                               |

| On State Input Voltage                                                       | 2.1    |           | 0.8        | v            |                                                                                          |

| Internal Pull-Up Voltage                                                     |        | 3.3       | 0.0        | v            |                                                                                          |

| Internal Pull-Up Resistance                                                  |        | 10        |            | kΩ           |                                                                                          |

| SERIAL IN                                                                    |        | 10        |            | nu l         |                                                                                          |

| Idle / Stop State Input Voltage                                              | 2.4    |           |            | V            |                                                                                          |

| Zero / Start State Input Voltage                                             |        |           | 0.8        | v            |                                                                                          |

| Internal Pull-Up Voltage                                                     |        | 3.3       |            | V            |                                                                                          |

| Internal Pull-Up Resistance                                                  |        | 10        |            | kΩ           |                                                                                          |

| SERIAL OUT                                                                   |        |           |            |              |                                                                                          |

| Idle / Stop State Output Voltage                                             | 2.9    | 3.1       |            | V            | 4 mA source current                                                                      |

| Zero / Start State Output Voltage                                            |        | 0.2       | 0.4        | V            | 4 mA sink current                                                                        |

| AC Good (AC GOOD)                                                            |        |           |            |              | Referenced to CTL RETURN                                                                 |

| AC Input Voltage for AC Good                                                 | 119    |           | 375        | Vpk          |                                                                                          |

| Low State Output Voltage                                                     |        | 0.2       | 0.4        | ý V          | 2 mA sink current                                                                        |

| Internal Pull-Up Voltage                                                     |        | 3.3       |            | V            |                                                                                          |

| Internal Pull-Up Resistance                                                  |        | 10        |            | kΩ           |                                                                                          |

| DC Good (DC GOOD)                                                            |        |           |            |              | Referenced to CTL RETURN                                                                 |

| Low State Output Voltage                                                     |        | 0.2       | 0.4        | V            | 2 mA sink current                                                                        |

| Internal Pull-Up Voltage                                                     |        | 3.3       |            | V            |                                                                                          |

| Internal Pull-Up Resistance                                                  |        | 10        |            | kΩ           |                                                                                          |

| WARN (positive logic)                                                        |        |           |            |              | Output shutdown warning                                                                  |

| Low State Output Voltage                                                     |        | 0.2       | 0.4        | V            | 2 mA sink current                                                                        |

| Internal Pull-Up Voltage                                                     |        | 3.3       |            | v            |                                                                                          |

| Internal Pull-Up Resistance                                                  |        | 10        |            | kΩ           |                                                                                          |

|                                                                              |        | 10        |            | 1/25         | 3.3 V output always on regardless of DEC ENA state                                       |

| 3.3V AUX<br>Output Voltage Range                                             | 3.19   | 3.30      | 3.43       | V            | 3.3 V output always on regardless of PFC ENA state<br>Over line, load, temp, and life    |

| 1 0 0                                                                        | 5.19   | 5.50      |            |              |                                                                                          |

| Source Current                                                               |        |           | 100        | mA           | Curchronization output at switching fragments                                            |

| SYNC OUT                                                                     | 2.0    | 2 1       |            | 14           | Synchronization output at switching frequency                                            |

| High State Output Voltage                                                    | 2.9    | 3.1       | 0.4        | V            | 4 mA source current                                                                      |

| Low State Output Voltage                                                     |        | 0.2       | 0.4        | V            | 4 mA sink current                                                                        |

| RELIABILITY CHARACTERISTICS                                                  |        | 662       |            |              | T 7000                                                                                   |

| Calculated MTBF (Telcordia)                                                  |        | 557       |            | kHrs         | $T_{B} = 70^{\circ}C$                                                                    |

|                                                                              |        |           |            |              |                                                                                          |

| Calculated MTBF (MIL-217) MIL-HDBK-217F<br>Calculated MTBF per MIL-HDBK-217F |        | 557<br>56 |            | kHrs<br>kHrs | Ground benign, $T_{B} = 70^{\circ}C$<br>Airborne Inhibited Cargo , $T_{B} = 70^{\circ}C$ |

Note 5: External input filter will contribute to this parameter.

Note 6: For use with droop share analysis. Assumes uniform thermal environment for modules in parallel.

Note 7: Tested according to section 16.7.5 of DO-160G. APFIC startup (t = 0) conducted at the AC voltage zero crossing (115 Vrms, 400Hz).

1-888-567-9596

APFIC-U-55xH-FG-x Input: 85-264 Vrms Output: 55 Vdc

**Power: 600 W**

**Technical Specification**

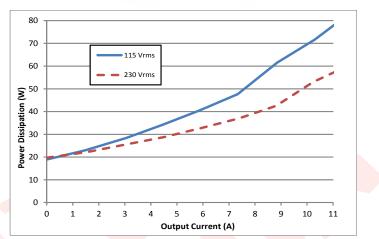

*Figure 1:* Efficiency at nominal output voltage vs. output current for 115Vrms and 230Vrms input voltage (applies to both 60Hz and 400Hz) at  $Tb = 25^{\circ}C$ .

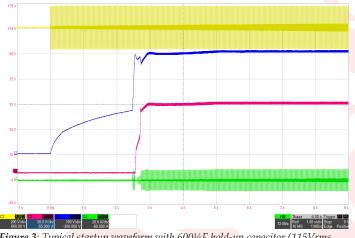

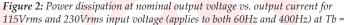

Figure 3: Typical startup waveform with 600¼F hold-up capacitor (115Vrms, 60Hz) Ch1: Vin (200V/div), Ch2: Vout (20V/div), Ch3: Hold-up capacitor voltage (100V/div), Ch4: Iin (20A/div), Timebase: (1s/div).

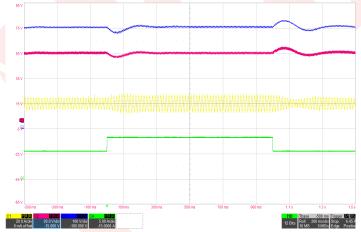

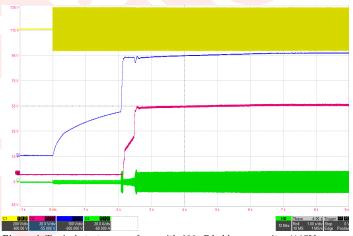

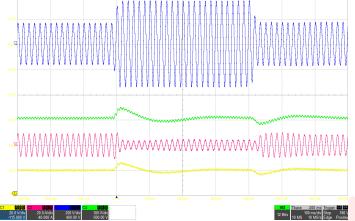

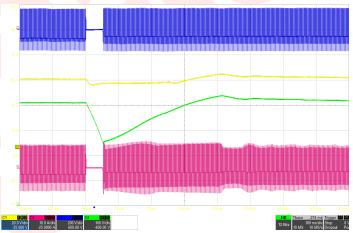

*Figure 5:* Load transient with  $600\mu$ F hold-up capacitor (50%-75%-50% of Imax, 115Vrms, 60Hz) Ch1: Iin (20A/div), Ch2: Vout (20V/div), Ch3: Hold-up capacitor voltage (100V/div), Ch4: Iout (5A/div), Timebase: (200ms/div).

**Figure 4:** Typical startup waveform with 600μF hold-up capacitor (115Vrms, 400Hz) Ch1: Vin (200V/div), Ch2: Vout (20V/div), Ch3: Hold-up capacitor voltage (100V/div), Ch4: Iin (20A/div), Timebase: (1s/div).

**Figure 6**: Load transient with  $600\mu$ F hold-up capacitor (50%-75%-50% of Imax, 115Vrms, 400Hz) Ch1: Iin (20A/div), Ch2: Vout (20V/div), Ch3: Hold-up capacitor voltage (100V/div), Ch4: Iout (5A/div), Timebase: (200ms/div).

# School of the second se

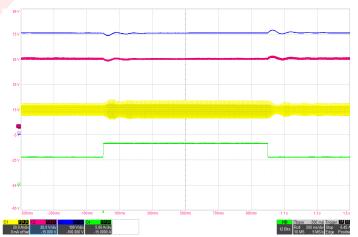

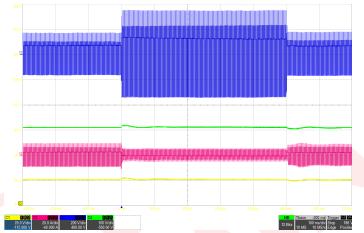

**Figure 7**: Input transient with  $600\mu$ F hold-up capacitor at full load (115Vrms-220Vrms-115Vrms, 60Hz) Ch1: Vout (20V/div), Ch2: Iin (20A/div), Ch3: Vin (200V/div), Ch4: Vhold-up (100V/div), Timebase: (100ms/div).

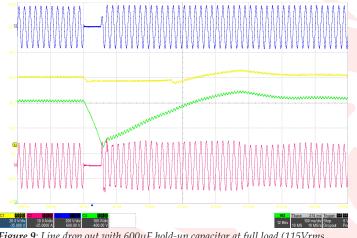

Figure 9: Line drop out with 600µF hold-up capacitor at full load (115Vrms, 60Hz) Ch1: Vout (20V/div), Ch2: Iin (10A/div), Ch3: Vin (200V/div), Ch4: Vhold-up (100V/div), Timebase: (100ms/div).

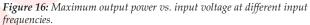

*Figure 11: Typical output voltage vs. output current for regulated and droop outputs.*

**Figure 8**: Input transient with  $600\mu$ F hold-up capacitor at full load (115Vrms-220Vrms-115Vrms, 400Hz) Ch1: Vout (20V/div), Ch2: Iin (20A/div), Ch3: Vin (200V/div), Ch4: Vhold-up (100V/div), Timebase: (100ms/div).

Figure 10: Line drop out with 600μF hold-up capacitor at full load (115Vrms, 400Hz) Ch1: Vout (20V/div), Ch2: Iin (10A/div), Ch3: Vin (200V/div), Ch4: Vhold-up (100V/div), Timebase: (100ms/div).

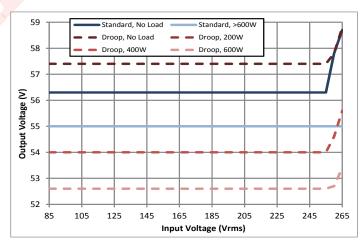

*Figure 12: Typical output voltage vs. input voltage for regulated and droop outputs at different output power.*

APFIC-U-55xH-FG-x Input: 85-264 Vrms Output: 55 Vdc

**Power: 600 W**

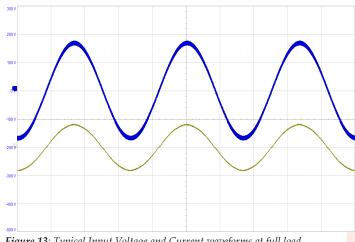

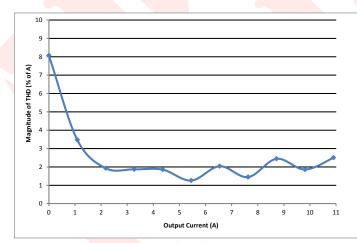

**Figure 13**: Typical Input Voltage and Current waveforms at full load current (115Vrms, 60Hz) Top: Vin (100V/div), Bottom: Iin (10A/div), Timebase: (5ms/div).

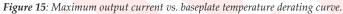

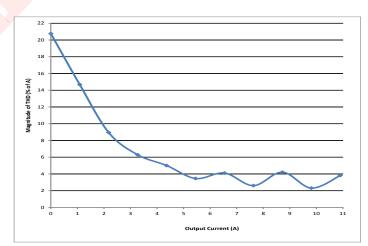

*Figure 17:* Total harmonic distortion (THD) at 115Vrms, 60Hz vs. output current (Tested with APFIC module and ACF-U-230-HT filter).

Figure 14: Typical Input Voltage and Current waveforms at full load current (115Vrms, 400Hz) Top: Vin (100V/div), Bottom: Iin (10A/div), Timebase: (1ms/div).

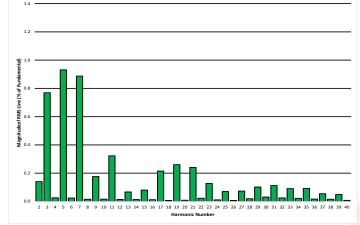

*Figure 18:* Total harmonic distortion (THD) at 115Vrms, 400Hz vs. output current (Tested with APFIC module and ACF-U-230-HT filter).

**Technical Specification**

APFIC-U-55xH-FG-x Input: 85-264 Vrms

Output: 55 Vdc **Power: 600 W**

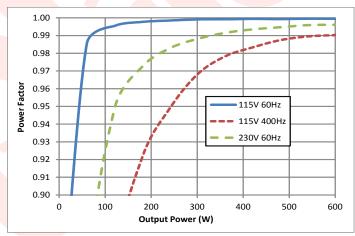

Figure 22: Power factor vs. output power at different input conditions, T=25°C (Tested with APFIC module and ACF-U-230-HT filter).

# 005-0007377

# **Standards & Qualification**

| Parameter            | Notes & Conditions |

|----------------------|--------------------|

| STANDARDS COMPLIANCE | Pending            |

| CE Marked            |                    |

Note: An external input fuse must always be used to meet these safety requirements. Contact SynQor for official safety certificates on new releases or download from the SynQor website.

| Parameter                             | # Units | Test Conditions                                                     |

|---------------------------------------|---------|---------------------------------------------------------------------|

| QUALIFICATION TESTING                 |         |                                                                     |

| Cold Temperature - Ground Survival    | 5       | RTCA/DO-160G Section 4.5.1                                          |

| Hot Temperature - Ground Survival     | 5       | RTCA/DO-160G Section 4.5.3                                          |

| Cold Temperature - Operating          | 5       | RTCA/DO-160G Section 4.5.2                                          |

| Hot Temperature - Operating           | 5       | RTCA/DO-160G Section 4.5.4                                          |

| Temperature Variation                 | 5       | RTCA/DO-160G Section 5.3.1                                          |

| Temperature Cycling                   | 5       | MIL-STD-810G Method 503.5 – Procedure I                             |

| Humidity                              | 3       | RTCA/DO-160G Section 6.3.1 (Category A)                             |

| Waterproofness - Condensing           | 3       | RTCA/DO-160G Section 10.3.1 (Category Y)                            |

| Fungus Resistance                     | 1       | MIL-STD-810G Method 508.6                                           |

| Vibration - Fixed Wing and Helicopter | 5       | RTCA/DO-160G Sections 8.5.2 (Level B4), 8.8.3 (Levels G and F1)     |

| Operational Shock and Crash Safety    | 5       | RTCA/DO-160G Section 7.2.1, 7.3.1, and 7.3.3 (Category B)           |

| Altitude - Steady State               | 2       | RTCA/DO-160G Section 4.6.1; 70,000 ft (21 km), see note             |

| Altitude - Decompression              | 2       | RTCA/DO-160G Section 4.6.2                                          |

| Loss of Cooling                       | 5       | RTCA/DO-160G Section 4.5.5                                          |

| Design Marginality                    | 5       | Tmin-10 °C to Tmax+10 °C, 5 °C steps, Vin = min to max, 0-105% load |

| Life Test                             | 5       | 95% rated Vin and load, units at derating point, 1000 hours         |

| Solderability                         | 15 pins | MIL-STD-883, Method 2003                                            |

Note: A conductive cooling design is generally needed for high altitude applications because of naturally poor convection cooling at rare atmospheres.

| Category Description                     | 115Vrms Specification Compliance                                                  |

|------------------------------------------|-----------------------------------------------------------------------------------|

| Input Voltage                            | 787B3-0147, D6-44588, Airbus ABD0100.1.8, RTCA/DO-160G                            |

| Switching Transients                     | 787B3-0147, D6-44588, Airbus ABD0100.1.8, RTCA/DO-160G, EN61000-4-4, EN61000-4-5  |

| Voltage Spikes                           | 787B3-0147, D6-44588, Airbus ABD0100.1.8, RTCA/DO-160G, EN61000-4-6               |

| Frequency Transients                     | 787B3-0147, D6-44588, Airbus ABD0100.1.8, RTCA/DO-160G                            |

| Harmonic Content                         | 787B3-0147, D6-44588, Airbus ABD0100.1.8, RTCA/DO-160G, EN61000-3-2, MIL-STD-1399 |

| DC Content on Input Voltage              | 787B3-0147, D6-44588, Airbus ABD0100.1.8, RTCA/DO-160G                            |

| Audio Frequency Conducted Susceptibility | D6-36440, RTCA/DO-160G                                                            |

| Audio Frequency Conducted Emissions      | D6-36440, RTCA/DO-160G                                                            |

| Induced Signal Susceptibility            | D6-36440, RTCA/DO-160G, EN61000-4-6                                               |

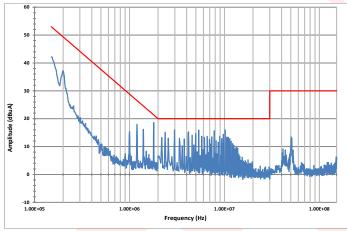

| Conductive Emissions                     | D6-36440, RTCA/DO-160G, EN55011/22                                                |

| Magnetic Effect                          | D6-36440, RTCA/DO-160G, EN61000-4-11                                              |

| Radiated Emissions                       | D6-36440, RTCA/DO-160G, EN61000-4-3                                               |

| Electrostatic Discharge                  | D6-36440, RTCA/DO-160G, EN61000-4-2                                               |

| Electrical Bonding and Grounding         | D6-36440, D6-44588, UL 60950-1                                                    |

| Lightning Requirements                   | D6-36440, D6-16050-5, RTCA/DO-160G                                                |

| Reliability                              | Telcordia, MIL-HDBK-217F                                                          |

# **Basic Operation & Features**

The APFICQor isolated power factor correction module is a high efficiency, high power AC-DC converter. It operates from a universal AC input to generate an isolated DC output voltage. Both regulated and semi-regulated (droop version) modules are available. As shown in **Figure A**, a typical power supply would be comprised of a SynQor AeroQor AC Line Filter, a SynQor APFICQor module and an energy storage hold-up capacitor. A fuse is needed to meet safety requirements.

One of the primary purposes of the APFICQor is to shape the input current that is drawn from a single-phase sinusoidal AC source into a nearly perfect sinusoidal waveform so that the AC-DC power supply will present a very high power factor load to this source. In doing this wave-shaping, the APFICQor ensures that the harmonic components of the AC current waveform are below the levels called for in testing standards. The total harmonic distortion of the AC current waveform is typically less than 3% at full load.

The APFICQor accomplishes its wave-shaping task by first rectifying the filtered AC source voltage, and then processing the input power through a non-isolated, high-efficiency, highfrequency "boost converter" that both gives the input AC current its sinusoidal shape and provides a regulated DC voltage across the hold-up capacitor. This stage is then followed by a highly efficient, fixed duty cycle isolation stage, which provides the isolated output voltage. For Regulated-output model, the output voltage is sensed and this information is sent to the primary side control circuitry through a digital isolator. The DC voltage across the hold-up capacitor is then adjusted to keep the output voltage regulated.

The hold-up capacitor handles the cyclic imbalance between the flow of energy drawn from the AC source and the flow of energy delivered to the load. This energy imbalance has a cyclic frequency twice that of the AC source voltage (e.g. 800Hz for a 400Hz input). This relatively low frequency makes the hold-up capacitor relatively large. Another purpose of the hold-up capacitor is to be a source of energy so that the output can continue to deliver load power during a temporary brownout or dropout of the AC source. A typical power supply will have sufficient hold-up capacitor to give a "hold-up time" in the 20ms range, but longer times can be achieved with yet more hold-up capacitance.

Besides shaping the AC current waveform, the APFICQor performs several other important functions. It has current limit controlled pre-charger that ensures input inrush current is nearly zero even with very large holdup capacitors. It has both output current limit and short circuit protection. It will also shut-down if the AC input voltage is out of its range (either too high or too low) for too long, or if the temperature of the module is too high.

In addition, the APFICQor has several control signals that are described in more detail below. It also has 3.3V AUX supply that can source up to 100 mA. All control signals and 3.3V AUX are secondary side referenced.

# Start-up Sequence

When the AC source voltage is first applied, regardless of whether the APFICQor is enabled or disabled through its PFC\_ENA pin, the APFICQor will pre-charge the output hold-up capacitor with a current limited to approximately 50 mA. If the APFICQor is enabled, this pre-charging continues until the hold-up voltage is higher than the peak voltage of the AC source. This actively controlled precharger limits the input inrush current to be nearly zero. If the APFICQor is disabled, the APFICQor will remain in the pre-charged state indefinitely. The typical hold-up voltage when disabled is about 180 V. It may vary with application.

When the PFC\_ENA input pin is pulled low, and after the pre-charging is completed if it is not already, the boost converter within the APFICQor will start operating and the APFICQor's hold-up voltage will be increased to its nominal regulated value. After this regulated voltage level is achieved, the isolation stage within the APFICQor will then start operating. The converter's output voltage will rise to its nominal value.

If the PFC\_ENA input is de-asserted (pulled high or allowed to float), the boost converter, as well as the isolation stage, in the APFICQor will shut down.

**NOTE:** Under extreme conditions, such as when 3.3V AUX is loaded with more than its rated current or power is being drawn from hold-up terminals, the pre-charger may not be able to charge the hold-up voltage above the peak voltage of the AC source. This may cause large inrush current when APFICQor attempts to turn on when it is enabled.

The voltage across the hold-up capacitor will remain in a charged state after the APFICQor is disabled as long as the AC source voltage is present.

# Brownout/Dropout Sequence

If the AC source voltage is present but it is below its continuous minimum input voltage limit, the APFICQor will still draw whatever power it can (within its current limit) from the AC source. This power may not be enough for the total load power, in which case the hold-up capacitor will provide the balance of the power.

# **Application Section**

The APFICQor hold-up module has control circuitry that will keep output voltage in regulation even as hold-up capacitor discharges. Using the maximum specified output capacitance on the hold-up module is recommended.

If and when the voltage across the hold-up capacitor drops below its specified minimum limit, the isolation stage will stop operating and output will be turned off. This condition will cause the APFICQor to return to the beginning of the startup sequence described above.

**NOTE:** Regardless of what happens to the APFICQor's holdup voltage under a brownout or dropout condition, if the AC source voltage drops below its rated under-voltage value for 1 second or more, the APFICQor will shut down.

If, however, the voltage across the hold-up capacitor does not drop below its specified minimum limit before the AC source voltage returns to within its continuous operating range (and it hasn't been absent for more than 1 second), the APFICQor will automatically re-establish its power flow. The hold-up capacitor will be recharged immediately to the peak of the AC source voltage (if it has fallen below this value) and to its nominal regulated voltage level within a few cycles of the AC source waveform.

**NOTE:** During the first phase where the hold-up capacitor is recharged (if this phase exists) there will be an inrush current drawn from the AC source that depends on the details of how quickly the AC source voltage returns to its normal operating condition.

#### **Control Features**

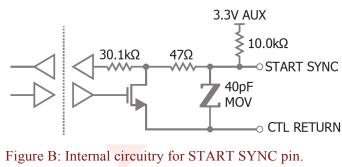

#### START SYNC (Pin A1):

Pin A1 is designated as START SYNC, and is only implemented on the Droop model. This pin is not used on the Regulated-output model and should be left floating when not used. In paralleled applications, connect START SYNC between multiple units to synchronize restart after a fault condition. Internal interface circuitry is shown in **Figure B**.

#### CTL RETURN (Pin A2):

CTL RETURN serves as the ground for all control signals. It is internal connected to VOUT- through  $5\Omega$  resistor.

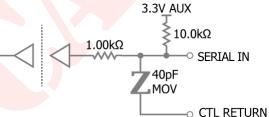

#### SERIAL IN (Pin A3):

A wide variety of operating parameter (voltages, currents, temperatures) may be accessed via the built-in full-duplex asynchronous serial interface. Commands may be transferred to the internal DSP via the SERIAL IN pin at 9600 baud (8N1 – 8 data bits, no parity, 1 stop bit). A 'start' or 'zero' bit in encoded as a logic low. The frequency tolerance of the external interface circuit should be better than  $\pm 2\%$  accuracy to ensure that the last bit of incoming serial data arrives within the proper frame time.

The SERIAL IN pin may be left open if unused, and will be internally pulled up to 3.3V AUX, corresponding to the 'idle' or 'stop' state. Internal circuitry is shown in **Figure C**. Direct connection may be made to an external microcontroller, but an external transceiver IC is required to shift levels and polarity to drive from a standard RS-232 port. See the separate "SynQor Single Phase Full-brick PFIC Terminal Commands" companion document for detailed syntax (available at www.synqor.com/Single Phase Full Brick\_PFIC Serial Interface).

Figure C: Internal circuitry for SERIAL IN pin.

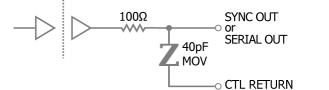

#### SERIAL OUT (Pin A4):

A response to each command is sent via the SERIAL OUT pin at 9600 baud (8N1 - 8 data bits, no parity, 1 stop bit). The output is low for a 'start' or 'zero' bit. When not transmitting, the output is high, corresponding to the 'idle' or 'stop' state. Internal circuitry is shown in **Figure D**. Direct connection may be made to an external microcontroller, but an external transceiver IC is required to shift levels and polarity to drive from a standard RS-232 port. See the separate "SynQor Single Phase Full-brick PFIC Terminal Commands" companion document for detailed command syntax (available at www.synqor.com/Single Phase Full Brick PFIC Serial Interface).

APFIC-U-55xH-FG-x # 005-0007377

Figure D: Internal circuitry for SYNC OUT and SERIAL OUT pins.

#### AC GOOD (Pin A5):

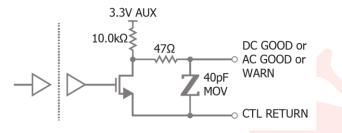

Internal interface circuitry for AC GOOD is shown in Figure E.

Figure E: Internal circuitry for AC GOOD, DC GOOD and WARN pins.

- The AC GOOD signal will be high whenever the AC source voltage is within the APFICQor's continuous operating range for at least one cycle of the source waveform, regardless of whether the APFICQor is enabled or disabled.

- When the peak of the AC source voltage is outside this continuous operating range (either too high or too low), the AC GOOD pin will be pulled low.

- The AC GOOD signal is typically used to indicate that the AC source voltage is no longer within the specified continuous operating range. The load power can only be delivered for the "hold-up time", and it may therefore be desirable to have the load gracefully shut down. The AC GOOD signal provides a warning for this action to be taken.

- When the AC source voltage returns to the specified continuous operating range, the AC GOOD signal will re-assert after a delay. The delay time is on the order of several hundreds of milliseconds. The exact timing is unspecified and varies with many factors such as input voltage, input frequency, and duration of input voltage being outside of the operating range.

#### DC GOOD (Pin A6):

Internal interface circuitry for DC GOOD is shown in Figure E. During start-up the positive-logic DC GOOD output will remain low until output voltage reaches its nominal value. It will remain high as long as isolation

stage is operating properly, therefore its falling threshold can be significant lower. The DC GOOD signal will usually remain high during an input power interruption. It is typically used to indicate successful startup, whereas AC GOOD is used to warn of an input power interruption.

#### PFC ENA (Pin A7):

The PFC ENA pin must be brought low to enable the unit. A  $10k\Omega$  pull-up resistor is connected internally to 3.3VAUX. Therefore, if all control pins are left floating, the unit be disabled. Internal interface circuitry is shown in Figure F.

WARN (Pin A8):

If the WARN pin is not externally held low, the pin will go high to warn of an impending over-temperature shutdown. The over-temperature warning engages 5°C below shutdown. A 10.0 k $\Omega$  pull-up resistor is connected internally to 3.3V AUX. Internal interface circuitry is shown in Figure E.

#### 3.3V AUX (Pin A9):

The 3.3V AUX supply (relative to CTL RETURN) can source up to 100 mA to power user loads. This independent supply is present and regulated whenever the APFICQor's hold-up voltage is greater than approximately 75V. The 3.3V AUX supply is unspecified when APFICQor's hold-up voltage is less than 75V (it may, for instance, come and go as the hold-up voltage rises on its way to 75V).

If unused, the 3.3V AUX output should be left open.

#### SYNC OUT (Pin A10):

The SYNC OUT pin generates a continuous series of pulses at the main switching frequency. The duty cycle is 50%. The boost and isolation stages are synchronized and switch at the same frequency. The SYNC OUT pin may be left open if not used. Internal interface circuitry is shown in **Figure D**.

### **Protection Features**

#### Input Over- and Under-Voltage:

If the AC source voltage exceeds the maximum peak voltage rating defined in the Electrical Specifications, the APFICQor will shut down. However, under this condition the APFICQor's pre-charge circuit will continue to deliver 50mA of current to the hold-up capacitor.

If a brownout or dropout of the AC source voltage occurs, and if it lasts long enough for the APFICQor's hold-up voltage to drop below its specified minimum limit, the APFICQor will shut down. Furthermore, regardless of what happens to the APFICQor's hold-up voltage, if the AC source voltage drops below its rated under-voltage value for 1 second or more, the APFICQor will shut down.

After any shutdown, the APFICQor will automatically return to the beginning of the startup sequence described above.

#### Hold-up Over-Voltage:

If the hold-up voltage exceeds its specified maximum limit, the APFICQor will remain active, but will stop delivering power through its main boost stage until the hold-up voltage falls below the over-voltage threshold. Under this condition, the isolation stage will remain active and provide output voltage.

# Output Current Limit and Short-Circuit Shutdown:

If the APFICQor's output is overloaded such that its output current limit becomes activated, the output voltage will fall as the excess load current discharges the hold-up capacitor. The APFICQor will continue to deliver power into this overload condition for about 1 second, after which the unit will shut down and automatically return to the beginning of the startup sequence described above. In above situations, both boost and isolation stage will turn off.

The APFICQor responds to a short-circuit event by turning the isolation stage off. The output voltage of the APFICQor will drop to zero. During the short circuit event, the boost converter will continue to run and the hold-up capacitor will remain charged. The module then enters a hiccup mode where it repeatedly turns on and off until the short-circuit condition is removed. This prevents excessive heating of the converter.

The off time during a short-circuit event is a function of input frequency. For 50/60Hz input, off time equals 25 line cycles. For example, at 60Hz, off time is:

$$T_{off(60Hz)} = \frac{25}{60} = 417ms$$

For 400Hz input, off time is 400 line cycles:

$T_{off(400Hz)} = \frac{400}{400} = 1000 ms$

#### **Over Temperature:**

If the internal temperature of the APFICQor reaches 125°C, the APFICQor will turn off its boost converter and isolation stage. When the internal temperature falls below 115°C, the APFICQor will return to the beginning of the startup sequence described above.

# Energy Storage Hold-Up Capacitor

The hold-up capacitor performs two functions:

- It handles the cyclic imbalance between the flow of energy drawn from the AC source and the flow of energy delivered to the load. In doing so, the voltage across the hold-up capacitor has a ripple at a frequency twice that of the AC source voltage (e.g. 800Hz for a 400Hz input). The larger the hold-up capacitor, or the higher the frequency of the AC source, the smaller this ripple will be.

- It provides a source of energy so that the APFICQor can continue to deliver load power during a temporary brownout or dropout of the AC source. The larger the hold-up capacitor the longer it can provide this energy. Often it will be made large enough to allow the load to be gracefully shutdown after the AC source has been outside of its normal range for a set amount of time. A typical "hold-up time" would be in the 20 ms range.

The total energy stored in a hold-up capacitor having capacitance C at any given voltage V is:

$$E = \frac{1}{2}CV^2$$

The amount of energy,  $\Delta E$ , which can be drawn from this capacitor depends on the capacitor's initial voltage,  $V_i$ , and its final voltage,  $V_f$ . This energy equals the amount of power, P, which the load draw through the isolation stage from the hold-up capacitor times the length of time,  $\Delta t$ , which it takes for the hold-up capacitor's voltage to drop from  $V_i$  to  $V_f$ . This energy can be equated to the hold-up capacitance according to the following formula:

$$\Delta \mathbf{E} = \frac{\mathbf{P}}{\eta_{ISO}} \Delta t = \frac{1}{2} \mathbf{C} (\mathbf{V}_1^2 - \mathbf{V}_1^2)$$

In this formula, P is the load power and  $\eta_{ISO} = 95\%$  is the

Rev. 2

Page 13

isolation stage efficiency. This formula can be rearranged to find the minimum required value for C to provide the hold-up time desired for a given power level.

$$\operatorname{Cmin} = 2 \frac{P}{\eta_{ISO}} \Delta t / (V_i^2 - V_r^2)$$

For example, if we assume P = 600W,  $\Delta t = 20$ ms, V<sub>i</sub> = 400V, Vf = 300V, and  $\eta_{ISO} = 95\%$ , then we would want a hold-up capacitance of at least 360µF.

**NOTE:** In the above example, the hold-up voltage drops by 25% at the end of brownout period. However, the output voltage will remain in regulation, see "Brownout/Dropout Sequence" for more detail.

**NOTE:** The APFICQor is able to operate with a minimum of  $100\mu$ F of hold-up capacitance, but SynQor recommends at least  $330\mu$ F if the power system will be required to conform to lightning surge standards. This is because the APFICQor relies on the hold-up capacitor to absorb most of the energy from a lightning surge.

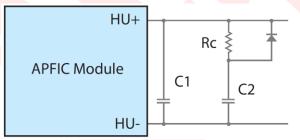

**NOTE:** Even though the APFICQor limits the inrush current drawn from the AC source during its startup sequence, it will not necessarily limit this current at the end of a temporary brownout or dropout of the AC source when the hold-up capacitor's voltage has not dropped below its minimum hold-up voltage limit. In such a condition the APFICQor will not reinitiate a startup sequence and it will therefore not limit the current flowing through it. If the peak of the AC source voltage is greater than the hold-up capacitor's voltage at the end of the brownout/dropout period, there will be a large inrush current for one half-cycle as the hold-up capacitor's voltage. The larger the hold-up capacitor, the larger this inrush current will be. To limit inrush current during this event, limit the charging current of additional hold-up capacitance with a resistor and diode as shown below.

If it is desired to have a hold-up time longer than can be achieved with the maximum specified hold-up capacitance, then the circuit shown below can be used.

In this circuit the total hold-up capacitance is (C1 + C2), and it can be made as large as desired as long as C1 does not exceed the maximum capacitance specified in the Technical Specifications table. The resistor, Rc, in series with C2 is present to limit the

current that will charge this capacitor after a temporary brownout/dropout event. Its resistance should be large enough to limit the charging current. The diode in parallel with the resistor permits the load converters to draw whatever energy they need from C2 without being hindered by the resistor.

#### **Output Ripple Considerations:**

The hold-up capacitor must have a ripple current rating high enough to withstand the ripple current generated on the hold-up capacitor of the APFICQor. Ripple current amplitude is dependent only upon the total APFICQor output power,  $P_{DC}$ , isolation stage efficiency  $\eta_{ISO} = 95\%$ , and the operating hold-up voltage  $V_{HU} = 400V$ . It can be calculated using the following formula:

$$Crms = \frac{P_{DC}}{\sqrt{2} \cdot \eta_{ISO} \cdot V_{HU}} = \frac{P_{DC}}{537}$$

The AC line frequency,  $f_{ac}$ , bulk capacitance, C, operating holdup voltage, and output power will determine the amplitude of the voltage ripple present on the output of the APFICQor. It can be calculated with:

$$V_{pk-pk} = \frac{P_{DC}}{2\pi \cdot \eta_{Iso} \cdot f_{ac} \cdot C \cdot V_{HU}}$$

At 400 Hz:  $V_{pk-pk} = \frac{P_{DC}}{9.55 \cdot 10^5 \cdot C}$

For example, to calculate the hold-up capacitor's voltage and current ripple for a APFICQor with a 600W output,  $600\mu$ F hold-up capacitor, and a 400Hz fundamental AC line frequency:

$$I_{Crms} = \frac{600W}{537} = 1.1A_{rms}$$

$$V_{pk-pk} = \frac{600W}{2\pi \cdot 0.95 \cdot 400 \cdot 600 \cdot 10^{-6}F \cdot 400V} = 1.0V_{pk-pk}$$

In this case, the hold-up capacitor would require a minimum ripple current rating of  $1.1A_{rms}$ , and the hold-up voltage would have a pk-pk ripple voltage of 1.4V, or 0.25%. Since the isolation stage is fixed duty cycle, the secondary output voltage will also have a 0.25% ripple at 2x the line frequency.

# 005-0007377

# Safety Notes

The output of the APFICQor is isolated from the AC source. However, the hold-up voltage and the control signals are primary-side referenced and are therefore hazardous voltages. Care must be taken to avoid contact with primary-side voltages, as well as with the AC source voltage. The APFICQor must have a fuse in series with its AC source. The rating for this fuse is given in the Technical Specification table.

# AeroOor AC Line Filter

An AC line filter is needed to attenuate the differential- and common-mode voltage and current ripples created by the APFICQor and the load, such that the system will comply with EMI requirements. The filter also provides protection for the APFICQor from high frequency transients in the AC source voltage. SynQor has a family of AC line filters that will provide these functions. It is recommended that a metal-oxide varistor (MOV) be placed from line-to-line on the input of the filter, and a TVS diode be placed from lineto-line on the output of the filter in order to keep the APFICQor input voltage from exceeding 450V during all transients, except when the APFICQor is disabled, when the input can tolerate 575V transients for up to 100 ms. See Figure A for example parts. If a non-SynQor AC line filter is used, the use of an MOV on the input and a TVS diode on the output of the filter is still recommended.

# **EMI** Considerations

To meet various conducted line emission standards, additional Y-capacitors may be needed to attenuate common-mode noise. SynQor recommends that safteyrated ceramic capacitors be placed from HU- to Vout- and Vout- to ground.

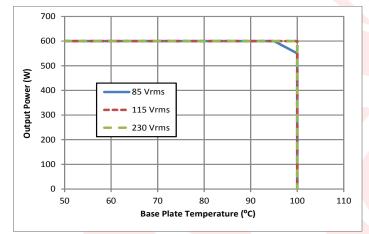

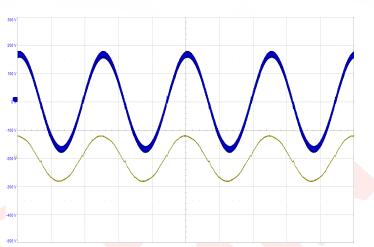

# Thermal Consideration

The maximum operating base-plate temperature,  $T_{B}$ , is 100°C. Refer to the thermal derating curves to see the allowable power output for a given baseplate temperature and input voltage. A power derating curve can be calculated for any heatsink that is attached to the base-plate of the converter. It is only necessary to determine the thermal resistance, RTHBA, of the chosen heatsink between the base-plate and the ambient air for a given airflow rate. The following formula can then be used to determine the maximum power the converter can dissipate for a given thermal condition:

$$P_{diss}^{max} = \frac{T_B - T_A}{R_{TH_{BA}}}$$

This value of power dissipation can then be used in conjunction with the data shown in the figures to determine the maximum load power that the converter can deliver in the given thermal condition.

# Paralleling Multiple APFICQors

In higher power applications, multiple droop version units can be used in parallel. Current share is accomplished by droop sharing method.

- START SYNC should be connected in parallel between all units in the system. SERIAL IN and PFC ENA input pins may be wired in parallel. AC GOOD and DC GOOD output pins may be wired in parallel.

- If the WARN protection-warning output function is used, then individual signals should be combined using an OR gate. If a WARN pin is not used, it may be left open.

- The 3.3V AUX outputs could be paralleled, but total current drawn should not exceed the rating of a single unit. SYNC OUT pins should not be connected between units.

# **Operation at High Input Voltages**

If the AC input voltage exceeds about 250 Vrms, both the hold-up voltage and output voltage may be raised up in order to maintain proper input current power factor correction. Output voltage can increase by up to 10% from the nominal output set point as input voltage increases from 250 Vrms to 264 Vrms. Refer to figure section for "Vout vs. Vin" chart under various conditions.

# 005-0007377

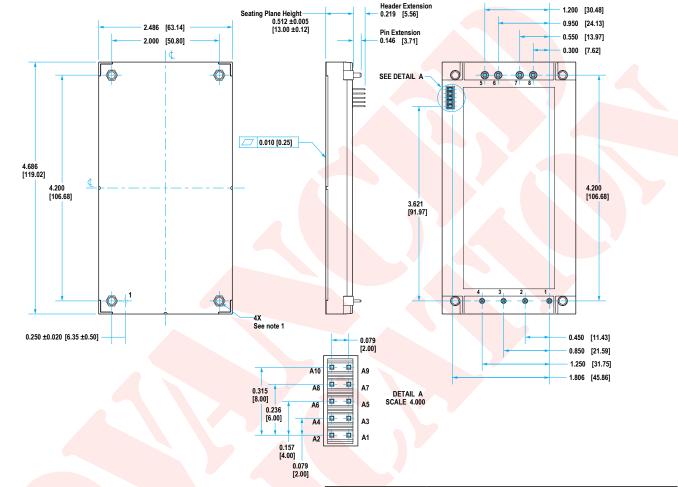

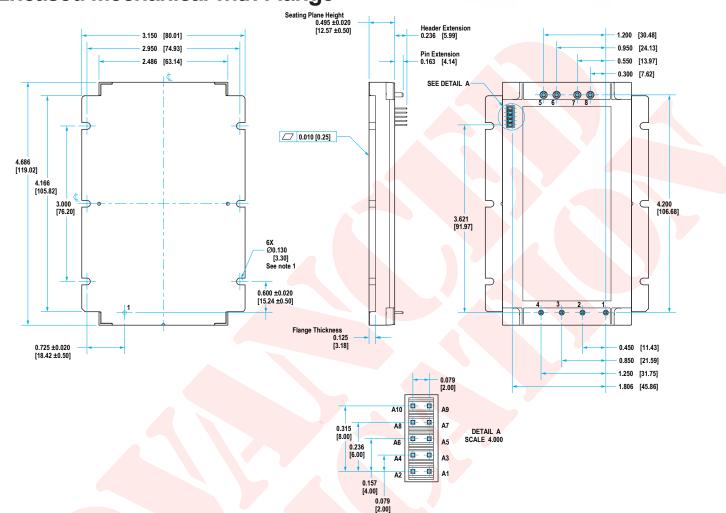

# **Encased Mechanical**

LICO

-

#### NOTES

Applied torque per M3 screw should not exceed 6in-lb. (0.7 Nm).

Baseplate flatness tolerance is 0.010" (.25 mm) TIR for surface.

Pins 5-8 are 0.080" (2.03 mm) diameter with 0.125" (3.18 mm)

- diameter standoff shoulder 4)Pins 1-4 are 0.040" (1.02 mm) diameter, with 0.080" (2.03 mm)

- diameter standoff shoulders.5)All Pins: Material Copper Alloy; Finish Matte Tin over Nickel plate

- 6)Undimensioned components are shown for visual reference only.

7)Weight: 11.3oz (320g)

8)Threaded and Non-Threaded options available 9)All dimensions in inches (mm).

Tolerances:

x.xx +/-0.02 in. (x.x +/-0.5mm)

x.xxx +/-0.010 in. (x.xx +/-0.25mm)

unless otherwise noted.

10)Workmanship: Meets or exceeds IPC-A-610C Class II

| PIN DESIGNATIONS |            |                                                          |  |  |

|------------------|------------|----------------------------------------------------------|--|--|

| Pin              | Name       | Function                                                 |  |  |

| 1                | L1         | AC Line 1                                                |  |  |

| 2                | L2/N       | AC Line 2 / Neutral                                      |  |  |

| 3                | HU+        | Positive Hold-up Voltage                                 |  |  |

| 4                | HU-        | Negative Hold-up Voltage                                 |  |  |

| 5                | VOUT-      | Negative Output Voltage                                  |  |  |

| 6                | VOUT-      | Negative Output Voltage                                  |  |  |

| 7                | VOUT+      | Positive Output Voltage                                  |  |  |

| 8                | VOUT+      | Positive Output Voltage                                  |  |  |

| A1               | RESERVED   | No Function (Regulated Output)                           |  |  |

|                  | START SYNC | Startup Synchronization (Droop Sharing)                  |  |  |

| A2               | CTL RETURN | Control Ground for A1-A10, Internally Connected to VOUT- |  |  |

| A3               | SERIAL IN  | Serial Data Input (High = Stop/Idle)                     |  |  |

| A4               | SERIAL OUT | Serial Data Output (High = Stop/Idle)                    |  |  |

| A5               | AC GOOD    | AC Power Good Output (High = Good)                       |  |  |

| A6               | DC GOOD    | DC Power Good Output (High = Good)                       |  |  |

| A7               | PFC ENA    | Pull Low to Enable Unit                                  |  |  |

| A8               | WARN       | High to Warn Impending OTP Shutdown                      |  |  |

| A9               | 3.3V AUX   | 3.3V @ 100mA Always-On Power Output                      |  |  |

| A10              | SYNC OUT   | Switching Frequency Synchronization Output               |  |  |

APFIC-U-55xH-FG-x

Input: 85-264 Vrms

Output: 55 Vdc Power: 600 W

# Encased Mechanical with Flange

**UnCor**

#### NOTES

1)Applied torque per M3 or 4-40 screw should not exceed 6in-lb. (0.7 Nm). 2)Baseplate flatness tolerance is 0.010" (.25 mm) TIR for surface.

- 3)Pins 5-8 are 0.080" (1.57 mm) diameter with 0.125" (3.18 mm) diameter standoff shoulder

- 4)Pins 1-4 are 0.040" (1.02 mm) diameter, with 0.080" (2.03 mm) diameter standoff shoulders.

- 5)All Pins: Material Copper Alloy; Finish Matte Tin over Nickel plate

- 6)Undimensioned components are shown for visual reference only.

- 7)Weight: 11.7oz (332g) 8)All dimensions in inches (mm).

- Tolerances:

- x.xx +/-0.02 in. (x.x +/-0.5mm)

- x.xxx +/-0.010 in. (x.xx +/-0.25mm)

- unless otherwise noted.

- 9)Workmanship: Meets or exceeds IPC-A-610C Class II

|     | PIN DESIGNATIONS |                                                          |  |  |  |  |

|-----|------------------|----------------------------------------------------------|--|--|--|--|

| Pin | Name             | Function                                                 |  |  |  |  |

| 1   | L1               | AC Line 1                                                |  |  |  |  |

| 2   | L2/N             | AC Line 2 / Neutral                                      |  |  |  |  |

| 3   | HU+              | Positive Hold-up Voltage                                 |  |  |  |  |

| 4   | HU-              | Negative Hold-up Voltage                                 |  |  |  |  |

| 5   | VOUT-            | Negative Output Voltage                                  |  |  |  |  |

| 6   | VOUT-            | Negative Output Voltage                                  |  |  |  |  |

| 7   | VOUT+            | Positive Output Voltage                                  |  |  |  |  |

| 8   | VOUT+            | Positive Output Voltage                                  |  |  |  |  |

| A1  | RESERVED         | No Function (Regulated Output)                           |  |  |  |  |

|     | START SYNC       | Startup Synchronization (Droop Sharing)                  |  |  |  |  |

| A2  | CTL RETURN       | Control Ground for A1-A10, Internally Connected to VOUT- |  |  |  |  |

| A3  | SERIAL IN        | Serial Data Input (High = Stop/Idle)                     |  |  |  |  |

| A4  | SERIAL OUT       | Serial Data Output (High = Stop/Idle)                    |  |  |  |  |

| A5  | AC GOOD          | AC Power Good Output (High = Good)                       |  |  |  |  |

| A6  | DC GOOD          | DC Power Good Output (High = Good)                       |  |  |  |  |

| A7  | PFC ENA          | Pull Low to Enable Unit                                  |  |  |  |  |

| A8  | WARN             | High to Warn Impending OTP Shutdown                      |  |  |  |  |

| A9  | 3.3V AUX         | 3.3V @ 100mA Always-On Power Output                      |  |  |  |  |

| A10 | SYNC OUT         | Switching Frequency Synchronization Output               |  |  |  |  |

APFIC-U-55xH-FG-x

Input: 85-264 Vrms

Output: 55 Vdc Power: 600 W

# Superior of the second second

# **Ordering Information**

|        | Part Numbering Scheme        |         |                                          |                     |                                        |         |  |

|--------|------------------------------|---------|------------------------------------------|---------------------|----------------------------------------|---------|--|

| Family | Input Voltage                | Output  | Regulation                               | Package Size        | Thermal Design                         | RoHS    |  |

|        |                              |         |                                          |                     | C: Encased                             |         |  |

| APFIC  | APFIC U: 85-264 Vrms 55:     | 55: 55V | RH: Regulated Holdup<br>DH: Droop Holdup | FG: Full-brick Giga | D: Encased with Non-threaded Baseplate | G: RoHS |  |

|        |                              |         |                                          |                     | V: Encased with Flanged Baseplate      |         |  |

| -      | Example: APEIC-U-55DH-EG-C-G |         |                                          |                     |                                        |         |  |

APFIC-U-55RH-FG-D-G

**RoHS Compliance:** The EU led RoHS (Restriction of Hazardous Substances) Directive bans the use of Lead, Cadmium, Hexavalent Chromium, Mercury, Polybrominated Biphenyls (PBB), and Polybrominated Diphenyl Ether (PBDE) in Electrical and Electronic Equipment. This SynQor product is 6/6 RoHS compliant. For more information please refer to SynQor's RoHS addendum available at our RoHS Compliance / Lead Free Initiative web page or e-mail us at rohs@synqor.com.

# Validation, Verification & Certification

#### USA Manufacturing Facility: AS9100 & ISO 9001 Certified

SynQor considers in-house manufacturing to be a core competency and strategic advantage. All SynQor products are manufactured in our manufacturing facility at our corporate headquarters in Boxborough, MA, USA, utilizing state-of-the art equipment and proprietary assembly techniques. By maintaining both AS9100 and ISO9001 certifications, SynQor is able to provide the same level of attention to detail in our manufacturing processes as we do in our products. We utilize proprietary in-house developed manufacturing data and document control systems that allow us to operate in a paperless manufacturing environment, providing both maximized manufacturing efficiency and flexibility. Ultimately, our manufacturing expertise remains in-house, allowing us to maintain complete control over the quality and traceability of our product down to the component level to meet the most stringent customer and industry requirements.

#### **Design, Engineering & Manufacturing Process**

SynQor employs a stringent, ECO controlled, 5-stage product development process, starting with product concept design and ending with manufacturing integration. We believe that a solid design and DFM review process leads to efficient manufacturing, higher performance, and enhanced reliability. By designing for reliability, SynQor greatly reduces the chance of field defects and increases product integrity.

| Concept Design                                                                                                                                                                                                                            | <b>Design &amp; Verification</b>                                                                                                                                                                                                                                                                                                             | Proof of Design                                                                                                                                                                                                                                                                        | Proof of Manufacturing                                                                                                                                                                                                                                                                                                                            | Manufacturing Integration                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Generate electrical<br/>specification</li> <li>Review performance<br/>requirements</li> <li>Design simulation</li> <li>Schematic</li> <li>Qualify new components</li> <li>Breadboard</li> <li>Prelim thermal analysis</li> </ul> | <ul> <li>Full layout</li> <li>DFM/DFT Review</li> <li>Build engineering<br/>prototypes</li> <li>Debug circuit</li> <li>Worst-case electrical<br/>testing</li> <li>Component stress<br/>analysis</li> <li>Stability analysis</li> <li>Abnormal electrical<br/>testing</li> <li>Specification review</li> <li>Preliminary datasheet</li> </ul> | <ul> <li>Build units and<br/>electrically characterize</li> <li>Verify electrical<br/>performance</li> <li>Verify component<br/>stress analysis</li> <li>Statistical variations</li> <li>Thermal analysis and<br/>imaging</li> <li>HALT testing</li> <li>Complete datasheet</li> </ul> | <ul> <li>Controlled Production<br/>Build</li> <li>ATE testing</li> <li>Yield analysis</li> <li>Validate and finalize<br/>manufacturing processes<br/>and Tooling</li> <li>1000 hour life test</li> <li>Qualification testing<br/>(humidity, vibration,<br/>DMT, PTC, thermal<br/>and mechanical shock,<br/>altitude and solderability)</li> </ul> | <ul> <li>Processes transfer</li> <li>Full documentation release<br/>(SCD's, BOM, processes,<br/>procedures, etc.)</li> <li>Release qualification reports</li> <li>Release final datasheet</li> <li>Transfer units to finished<br/>goods</li> </ul> |

#### Contact SynQor for further information and to order:

| Phone:     | 978-849-0600                |

|------------|-----------------------------|

| Toll Free: | 888-567-9 <mark>5</mark> 96 |

| Fax:       | 978-849-0602                |

| E-mail:    | power@synqor.com            |

| Web:       | www.synqor.com              |

| Address:   | 155 Swanson Road            |

|            | Boxborough, MA 01719        |

|            | USA                         |

|            |                             |

#### PATENTS

SynQor holds numerous U.S. patents, one or more of which apply to most of its power conversion products. Any that apply to the product(s) listed in this document are identified by markings on the product(s) or on internal components of the product(s) in accordance with U.S. patent laws. SynQor's patents include the following:

6,896,526 6,927,987 7,050,309 7,085,146

7,765,687 7,787,261 8,149,597 8,644,027

#### WARRANTY

SynQor offers a two (2) year limited warranty. Complete warranty information is listed on our website or is available upon request from SynQor.

# 005-<u>0007377 \_\_\_</u>

Rev. 2

1-888-567-9596